Đọc chậm thôi nha: Các mạch xử lý dữ liệu trong AGC hoạt động thế nào với Core Rope-P2

Bài này tập trung vào lớp “bảng mạch” đó. Ý tưởng là đi cùng anh em từ địa chỉ 12 bit mà lệnh AGC dùng, qua lớp logic NOR RTL, xuống đến các transistor bơm dòng vài trăm milliampere trên dây set/reset, rồi ngược lại lên các IC khuếch đại sense nhặt những xung nhỏ xíu trên dây sense và trả về cho CPU một word 16 bit hoàn chỉnh. Toàn bộ hành trình đó diễn ra trong vài micro‑giây mỗi lần đọc, lặp lại hàng triệu lần suốt một sứ mệnh Apollo.

Cấu trúc của máy tính dẫn đường Apollo (theo chiều kim đồng hồ từ góc trên bên trái): Trái tim của hệ thống là các dãy mạch tích hợp – những vi mạch đầu tiên từng được sử dụng trong một chiếc máy tính. Chúng được lắp ráp thành các module logic đặt sát cạnh nhau. Các diode đảm nhiệm việc chuyển mạch thông tin. Toàn bộ các mạch điện trong máy được nối với nhau bằng khoảng 4.000 sợi dây.

Mạch giải mã địa chỉ: từ 12 bit đến module, lõi và strand

Ở tầng phần mềm, mỗi lệnh của AGC có thể chứa một địa chỉ 12 bit. Nếu chỉ dùng 12 bit, không gian địa chỉ trực tiếp chỉ là 4K word (2^12 = 4096), trong khi toàn bộ bộ nhớ của AGC gồm 36K word core rope ROM và 2K word core RAM, tổng cộng là 38k. Để giải quyết sự khác biệt này, hệ thống sử dụng thêm các thanh ghi bank và một lớp logic giải mã địa chỉ (address decoding) tương đối phức tạp, nằm chủ yếu trên “A‑tray” cùng với logic CPU. Điều này, kết hợp với 12 bit địa chỉ, cho phép CPU có thể “nhìn sang” nhiều khối nhớ 4K khác nhau, tổng cộng phủ được 36K ROM + 2K RAM.Nhiệm vụ của mạch giải mã địa chỉ là ba bước. Thứ nhất, nó quyết định truy cập hiện tại đang hướng đến RAM có thể thay đổi hay ROM lưu trữ cố định trong core rope. Thứ hai, nếu là core rope, nó phải xác định đó là bank nào, module nào trong sáu module, và mặt phẳng (plane) nào trong module đó. Thứ ba, nó phải tạo ra các tín hiệu cần thiết để chọn được một lõi cụ thể và một strand cụ thể trong lõi đó. Nói cách khác, nó nhận vào “địa chỉ logic” mà lập trình viên thấy, rồi “dịch” thành tọa độ vật lý: module số mấy, plane nào, lõi thứ bao nhiêu, word thứ mấy trên lõi đó.

Về mặt phần cứng, toàn bộ logic này được xây dựng từ một loại IC khá nguyên sơ: mỗi chip chứa hai cổng NOR sử dụng công nghệ RTL (resistor‑transistor logic). Nói kĩ một chút thì cổng NOR là một cổng logic nhận nhiều ngõ vào, chỉ cho ra 1 khi tất cả ngõ vào đều là 0; hễ có ít nhất một ngõ vào là 1 thì ngõ ra là 0. Đây là một cổng “đa năng” vì nếu ghép nhiều cổng NOR với nhau, anh em có thể xây được mọi hàm logic khác (AND, OR, NOT, v.v.).

Và trong AGC, từ những cổng NOR cơ bản, gần như toàn bộ logic số được dùng để lắp ghép thành các mạch giải mã, mạch chọn bank, mạch tạo tín hiệu điều khiển cho dây inhibit, set, reset, clear và các đường chọn strand. Giả định mỗi core rope có 4K hoặc 8K word, mạch giải mã địa chỉ có thể được xử lý rất gọn, một số bit cao trong địa chỉ dùng để chọn module (module 0, 1, 2…), tiếp theo, các bít thấp còn lại dùng để chọn word bên trong. Khi đó, chỉ cần vài dòng dây là đủ.

Tuy nhiên, mỗi core rope module chứa 6K word như giải thích ở bài trước, không phải một lũy thừa của 2 như 4K, 8K, nên việc biến các bit địa chỉ thành “module select” và “strand select” không thể chỉ là cắt gọn đẹp theo biên giới nhị phân; thay vào đó, logic NOR phải được thiết kế để nhận diện từng dải địa chỉ cụ thể, ví dụ địa chỉ từ A đến B thì kích module 0, từ C đến D thì kích module 1, v.v., kết hợp với bit bank để biết đang ở khối 4K nào trong tổng 38K word. Sau khi biết module nào đang được chọn, các bit địa chỉ còn lại mới được dùng để sinh ra “strand select”, tức là chọn 1 trong 12 word trong mỗi lõi và các pattern inhibit tương ứng với từng lõi cụ thể trong module.

Một chi tiết thú vị là AGC chỉ dùng hai loại IC chính: IC sense amplifier cho mạch tương tự, và IC dual NOR cho toàn bộ logic số, bao gồm mạch giải mã địa chỉ lẫn CPU. Vào đầu thập niên 1960, việc xây nguyên cả CPU và subsystem bộ nhớ bằng IC là rất tiên phong; AGC trở thành một trong những khách hàng tiêu thụ IC lớn nhất thế giới giai đoạn 1962–1965, đủ sức tác động đến cả ngành công nghiệp bán dẫn.

Bảng mạch Strand select: bật đúng “kênh” word ra khỏi lõi

Ở bài trước, anh em đã thấy mỗi lõi trong core rope của AGC có 192 dây sense gắn logic với nó, chia thành 12 nhóm 16 dây, mỗi nhóm gọi là một strand và tương ứng với một word 16 bit (15 bit dữ liệu + 1 bit parity). Khi một lõi lật trạng thái, tất cả dây sense đi xuyên qua lõi đó đều nhận xung, nhưng AGC không muốn đọc cả 12 word cùng lúc; nó chỉ cần đúng một word theo địa chỉ. Phần việc “chọn bó dây nào được nói” được thực hiện bởi một module riêng: bảng mạch strand select.

Mạch giải mã địa chỉ, sau khi xác định được word cần đọc nằm trên strand số mấy, sẽ xuất ra tín hiệu logic “strand select” tương ứng, tức một hoặc vài đường điện áp ở mức tương ứng với “1” (active) cho strand đó và “0” (inactive) cho các strand khác. Module strand select nhận những tín hiệu mức logic này và dùng các tầng transistor NPN/PNP để tạo ra các xung điện áp khoảng 14 V trên các đường chọn, đủ mạnh để điều khiển mạng điện trở‑diode bên trong module rope. Về cấu trúc, mỗi module strand select chứa nhiều kênh driver, mỗi kênh nối với một đường chọn strand của core rope; điện trở trong mạch được chọn tay kỹ càng để đảm bảo dòng và điện áp ở mức chính xác.

Bên trong mỗi module core rope, các dây sense không đi thẳng ra sense amplifier, mà chúng đi qua một mạng điện trở và diode được bố trí dày đặc xung quanh khối lõi, theo cấu trúc “cordwood”, tức linh kiện cắm đứng xuyên qua module, hai đầu lộ ra hai phía. Với cấu trúc này, thay vì gắn linh kiện (điện trở, diode) nằm ngang trên một mặt PCB như bình thường, người ta khoan lỗ rồi cắm linh kiện theo chiều dọc, xuyên từ mặt này sang mặt kia của khối module. Phần chân/đầu linh kiện sẽ hàn vào mạch in ở cả hai bên, nên nhìn từ ngoài, một đầu linh kiện lộ ra ở mặt A, đầu còn lại lộ ra ở mặt B, giống như một que tăm xuyên qua một khối gỗ, hai đầu que đều thò ra ngoài.

Khi một đường chọn strand được kéo lên mức 14 V từ module strand select, các diode trong mạng tương ứng với 16 dây của strand đó sẽ phân cực thuận và cho dòng chạy qua biến áp sense, trong khi diode của 11 strand còn lại bị phân cực ngược và chặn dòng. Như vậy, ở thời điểm đọc, chỉ duy nhất 16 dây sense của strand được chọn là thực sự “nói chuyện” với sense amplifier; số dây còn lại, dù có thể mang xung (vì cũng xuyên qua lõi vừa lật), vẫn bị cô lập trong module.

Anh em có thể tưởng tượng, nếu ví core rope như một bó 12 đường loa cắm chung vào một ampli, thì strand select chính là mạch công tắc điện tử chọn xem “bật loa nào”: nhận lệnh chọn, đẩy điện áp lên đúng đường, mở đường cho tiếng nói của nhóm dây đó, và tắt mọi kênh khác.

Rope driver: khuếch đại công suất cho set, reset, inhibit, clear

Để một lõi từ có thể lật trạng thái đáng tin cậy, dòng điện chạy trên dây set hoặc reset phải đủ lớn và có dạng xung phù hợp. Trong AGC, dòng này có thể lên tới khoảng 450 mA đối với một số đường, con số khá đáng kể nếu so với tín hiệu logic bình thường. Mặt khác, các dây inhibit, dù không cần dòng lớn bằng, vẫn phải được điều khiển chính xác vì chúng chịu trách nhiệm triệt từ trường tại những lõi không được chọn. Toàn bộ phần chức năng này được đảm nhiệm bởi các module rope driver, thường có hai module trong hệ thống cho core rope.Mạch giải mã địa chỉ tạo ra các tín hiệu logic mức thấp (0/1) cho biết: bật set trên plane nào, reset plane nào, dây inhibit nào cần có dòng cùng chiều hoặc ngược chiều, có cần clear toàn bộ lõi trong module hay không. Rope driver nhận các tín hiệu này và dùng các tầng transistor NPN/PNP ghép tầng cùng với điện trở chọn tay để tạo ra xung dòng có biên độ chính xác trên từng dây trong module rope. Việc chọn từng giá trị điện trở là cực kỳ quan trọng: nếu dòng quá thấp, lõi có thể không lật; nếu dòng quá cao, dễ gây bão hòa, tăng nhiễu, hoặc căng thẳng nhiệt trên linh kiện.

Ngoài transistor và điện trở, rope driver còn sử dụng các cuộn cảm để “định hình” xung. Xung dòng quá dốc, tức dòng tăng từ 0 lên giá trị cần thiết (rise time) hoặc giảm về 0 (fall time) gần như ‘dựng đứng’ trong một khoảng thời gian rất ngắn thay vì từ từ. Xung có cạnh quá dốc tạo ra phổ tần số cao mạnh hơn, dễ gây nhiễu điện từ rất mạnh, cảm ứng lên dây sense và các mạch lân cận, khiến sense amplifier khó phân biệt đâu là xung do lõi lật, đâu là nhiễu. Bằng cách chèn cuộn cảm vào đường xung, các cạnh xung được “mềm hóa” theo thiết kế, vừa đủ nhanh để không làm chậm bộ nhớ, vừa đủ êm để hạn chế nhiễu. Trong các module rope driver, người ta bố trí nhiều nhánh mạch khác nhau: nhánh cho set, nhánh cho reset từng plane, nhánh cho inhibit theo từng bit địa chỉ, và nhánh cho clear. Mỗi nhánh có đặc điểm về biên độ và thời lượng xung riêng, nhưng tất cả đều được thiết kế sao cho đáp ứng chuẩn timing của AGC, tức bộ các yêu cầu về thời gian mà mọi xung set, reset, inhibit, clear phải tuân theo để hệ thống hoạt động đúng.

Một chi tiết thú vị khác là AGC có thêm một cặp dây inhibit dành riêng cho parity địa chỉ. Điều này đảm bảo rằng mọi lõi không được chọn đều nhận ít nhất hai tín hiệu inhibit, giúp “khóa” chúng chắc chắn hơn. Nếu chỉ có một inhibit bị kích, một lõi ở rất gần ngưỡng có thể nhận chút dòng dư và từ trường của nó bị “xê dịch” nhẹ, gây nhiễu về sau; thêm inhibit thứ hai làm biên độ triệt dòng mạnh hơn, ổn định hơn. Tất cả những tinh chỉnh như vậy đều được phản ánh trong thiết kế rope driver.

Sense amplifier: bắt xung rất nhỏ giữa biển nhiễu

Ở phía đọc, nơi mạch chỉ “lắng nghe” các xung rất nhỏ được cảm ứng trên dây sense khi lõi lật, nhiệm vụ khó nhằn nhất là mạch sense amplifier. Mỗi khi một lõi lật trạng thái từ hóa, sự thay đổi từ trường của nó cảm ứng một xung điện áp nhỏ trên từng dây sense đi xuyên qua lõi đó. Với các lõi khá lớn dùng trong core rope AGC, xung này có biên độ cỡ vài trăm millivolt, nhưng vẫn rất nhỏ so với xung trên dây set/reset và so với nhiễu chung trong hệ thống. Thời gian xung cũng rất ngắn, nên nếu không xử lý cẩn thận, xung có thể bị “chìm nghỉm” trong nhiễu hoặc biến dạng đến mức khó phân biệt được.Để giải quyết, mỗi dây sense được nối vào một biến áp nhỏ trước khi đi vào IC sense amplifier. Biến áp này tạo ra hai tín hiệu đối xứng, và sense amplifier hoạt động theo kiểu khuếch đại vi sai: nó không đo một đầu dây so với mass như kiểu khuếch đại thông thường (single‑ended), nơi nhiễu chung trên cả hệ thống chồng thẳng lên tín hiệu, mà đo sự chênh lệch giữa hai đầu dây

Với khuếch đại vi sai, anh em có hai dây: khi lõi lật, điện áp trên hai dây biến đổi ngược chiều nhau, tạo ra một độ chênh lệch; còn nhiều loại nhiễu chung sẽ làm cả hai dây cùng nhúc nhích gần như giống nhau. Mạch vi sai chỉ khuếch đại phần “chênh lệch giữa hai đầu”, nên tự động triệt tiêu những thứ tác động giống nhau lên cả hai, nhờ đó bắt xung nhỏ dễ hơn trong biển nhiễu. Trong khi đó, xung do lõi lật tạo ra sẽ làm lệch cân bằng giữa hai phía, tạo nên một tín hiệu vi sai rõ ràng mà sense amplifier có thể khuếch đại.

Các IC sense amplifier của AGC là loại chip analog tùy chỉnh, được thiết kế khoảng năm 1962 bởi Sperry Rand, và có thể xem là nằm trong nhóm IC khuếch đại chuyên dụng sớm nhất. Mỗi IC chứa mạch tiền khuếch đại, các tầng lọc, một mạch ngưỡng để quyết định “đủ lớn để coi là 1” và mạch out driver để đưa kết quả ra dạng logic cho CPU. Các module sense amplifier còn tích hợp thêm mạch ổn áp cục bộ, vì ngưỡng nhận xung và độ tuyến tính của khuếch đại phụ thuộc rất nhiều vào mức nguồn sạch và ổn định. Trên thực tế, một module sense amp có 16 kênh khuếch đại, nhưng chỉ một nửa số transistor output được dùng cho ROM, nửa còn lại cho RAM; hai module giống hệt nhau được đặt ở slot B13 (RAM) và B14 (ROM), và đầu ra của chúng được ghép với nhau để tạo thành bus dữ liệu 16 bit.

Một thách thức nữa là hướng của xung trên dây sense có thể khác nhau tùy theo cách dây sense đi cùng hay ngược chiều với dây set/reset qua các lõi khác. Nghĩa là khi lõi lật, xung trên dây sense có thể là “dương” hay “âm” so với một chuẩn nào đó. Sense amplifier vì thế phải được thiết kế để nhận cả hai loại xung lưỡng cực, rồi mạch ngưỡng sẽ chuyển thành một quyết định nhị phân: “có xung đáng kể” thì coi là 1, “không có xung” thì là 0, bất kể xung ban đầu đi lên hay đi xuống. Phần này làm cho thiết kế analog của sense amplifier vừa phức tạp, vừa thú vị nếu nhìn từ góc độ kỹ sư điện tử.

Tóm tắt lại chu kỳ đọc word từ core rope

Khi ghép tất cả các module trên lại, đường đi của một word từ core rope vào CPU trông như sau. CPU thực thi lệnh, cần đọc một word ở địa chỉ nào đó trong ROM; nó đưa ra địa chỉ logic 12 bit cùng với trạng thái bank. Mạch giải mã địa chỉ đọc các bit này, quyết định đây là truy cập core rope, chọn đúng module và plane, tạo ra pattern tín hiệu cho dây inhibit, dây set/reset/clear, và chọn luôn strand tương ứng với word cần đọc.Các tín hiệu logic này đi đến rope driver, nơi chúng được biến thành những xung dòng mạnh trên dây set, reset, inhibit, clear bên trong module core rope. Nhờ thiết kế của hệ inhibiting, chỉ đúng một lõi trong toàn bộ mặt phẳng được chọn là thực sự lật trạng thái từ hóa; mọi lõi khác đều bị ít nhất một cặp inhibit triệt không cho lật, đảm bảo không tạo xung “rác” trên dây sense. Cùng lúc đó, module strand select dùng các tầng transistor của mình kéo đường chọn của strand cần đọc lên mức 14 V, mở mạng diode‑điện trở bên trong module rope cho đúng 16 dây sense của strand đó “thông” tới biến áp sense, còn 176 dây sense còn lại dù có xung vẫn bị cô lập.

Khi lõi được chọn lật, 16 dây sense đi xuyên qua lõi đó trong strand được chọn nhận xung điện áp nhỏ; dây nào không xuyên qua lõi thì im lặng. Những xung này chạy qua biến áp sense, bị sense amplifier “bắt” và khuếch đại, lọc nhiễu nền, xử lý cả trường hợp xung dương hoặc âm; sau cùng, mỗi kênh sense amplifier đưa ra một mức logic 0 hoặc 1 tương ứng với việc có xung hay không. 16 bit này, bao gồm 15 bit dữ liệu và 1 bit parity, được ghép thành một word hoàn chỉnh trên bus dữ liệu và gửi vào CPU. Từ góc nhìn của mã máy, mọi chuyện chỉ là: CPU đọc một địa chỉ ROM và nhận lại một word; nhưng phía sau là cả một dàn mạch logic và analog phối hợp rất chặt chẽ.

Nhờ thiết kế đó, core rope trở thành một loại ROM cực kỳ tin cậy: dữ liệu được cố định bằng đường đi của dây, nên không lo mất dữ liệu do nhiễu, bức xạ hay lỗi phần mềm; mạch lái và mạch khuếch đại được thiết kế để đảm bảo mỗi lần đọc lõi đều sáng, mạnh, không nhầm lẫn. Chính sự kết hợp giữa dệt thủ công và mạch điện tử tinh vi này đã cho phép Apollo Guidance Computer mang theo cả “bộ não” của một nhiệm vụ lên Mặt Trăng trong một thể tích chưa tới một feet khối, với độ tin cậy đủ để NASA dám đặt cược cả sứ mệnh vào nó.

Tin xem thêm

Hướng dẫn truy cập và thiết lập máy tính Perplexity?

MXH mygo - Hướng dẫn truy cập và thiết lập máy tính Perplexity?

8 quy tắc bất ngờ tại Met Gala, từ lời mời đến việc ai sẽ trả tiền vé 100.000 đô la...

MXH mygo - 8 quy tắc bất ngờ tại Met Gala, từ nghi thức mời đến việc ai sẽ trả tiền vé 100.000 đô la...

Taxi bay thử nghiệm tại New York: thời gian bay 7 phút!

MXH mygo - Taxi bay thử nghiệm tại New York: thời gian bay 7 phút!

Samsung phát triển màn hình holographic, có thể dành cho iPhone

TinhTe/Anh Tú - Samsung phát triển màn hình holographic, có thể dành cho iPhone

Lộ diện thiết kế và cấu hình Samsung Galaxy Glasses: Đối thủ của Meta Ray-Ban

TinhTe/Anh Tú - Lộ diện thiết kế và cấu hình Samsung Galaxy Glasses: Đối thủ của Meta Ray-Ban

Tổng thống Trump dự định mời Tim Cook và các CEO lớn thăm Trung Quốc

TinhTe/Anh Tú - Tổng thống Trump dự định mời Tim Cook và các CEO lớn thăm Trung Quốc

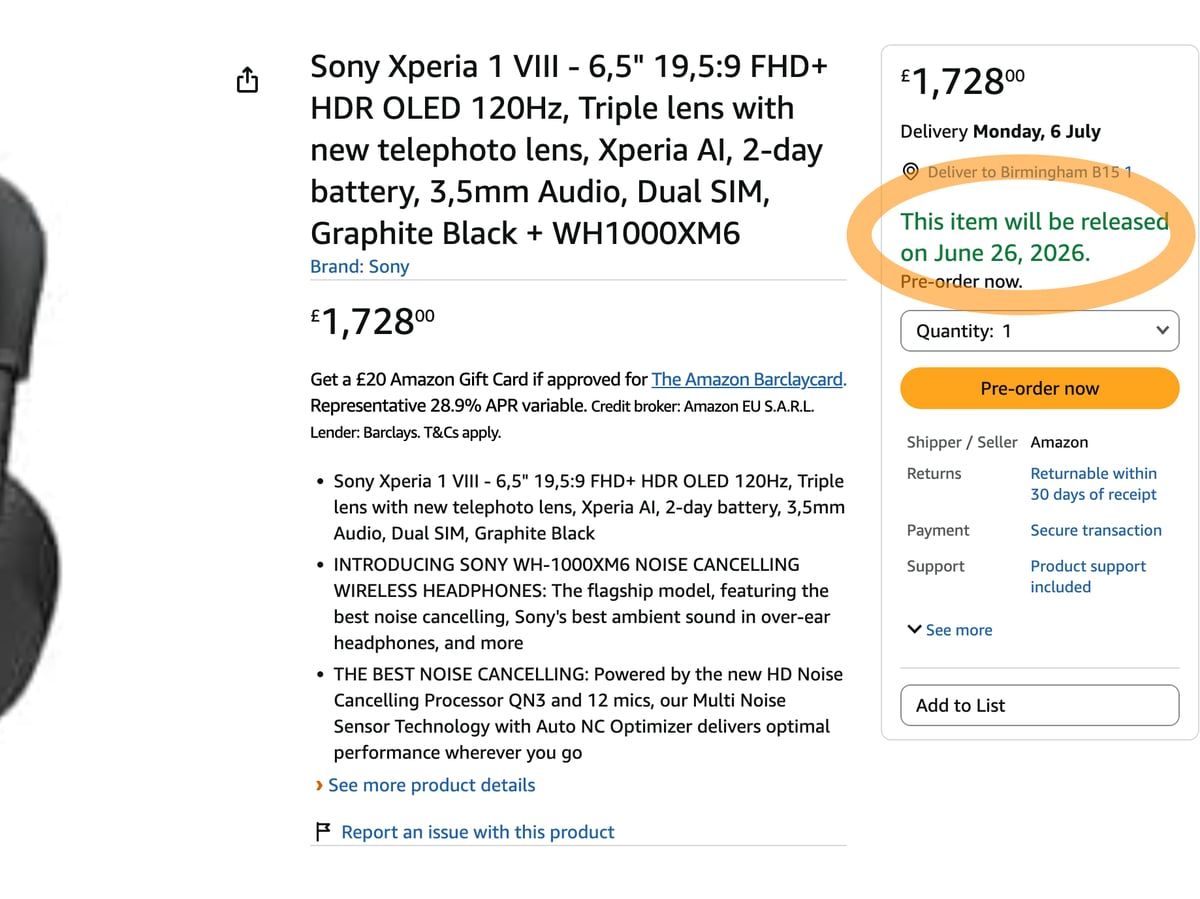

Sony Xperia 1 VIII có khả năng ra mắt 26/6/2026 cùng mức giá 53.6 triệu đồng?

TinhTe/Lâm Huy - Sony Xperia 1 VIII có khả năng ra mắt 26/6/2026 cùng mức giá 53.6 triệu đồng?

Samsung Odyssey G8 5K sắp bán tại Việt Nam, Dual Mode 180Hz–360Hz

TinhTe/Trung DT - Samsung Odyssey G8 5K sắp bán tại Việt Nam, Dual Mode 180Hz–360Hz

Xiaomi 18 Ultra có thể dùng chip tự phát triển Xring O3, xung nhịp vượt 4GHz

TinhTe/Anh Tú - Xiaomi 18 Ultra có thể dùng chip tự phát triển Xring O3, xung nhịp vượt 4GHz

nội dung mới